# **Create and Put Into Use a Fast-Firing Transistor (Fft) Processor That Has a High Throughput, Minimal Complexity, and Maximum Area Utilization**

Mohit Tyagi, Electronics and Communication Engineering, R.D Engineering College, Duhai, Ghaziabad, UP. India

Corresponding Author- [tyagi.mohit@gmail.com](mailto:tyagi.mohit@gmail.com)

## **Abstract**

Modern wireless technologies get even more benefits from using FFT processors to handle data, such as reduced circuit complexity, fast speed, and low power consumption. Building a high-performance FFT architecture is, hence, crucial to satisfy the real-time requirements. This paper aims to synthesise two 8-point fast Fourier transform (FFT) processors into a single 16-point radix-2 based decimation-in-frequency (DIF) processor. We used ModelSim to model the new 16-point DIF-FFT architectural design, and Xilinx ISE Project Navigator for hybrid synthesis. In this comparison, we look at the synthesis reports of both the current and proposed designs. In conclusion, the results of the comparisons reveal that the suggested 16-point DIF-FFT design uses less power, is faster, and makes better use of memory. Therefore, any application requiring low power and high speed operation may make advantage of the suggested design.

**Keywords:** Fast Fourier Transforms, Xilinx with ModelSim

## **Introduction**

One of the most common methods for modifying data sequences in Fourier analysis is the Fourier transform. It translates functions from the time domain into their frequency domain equivalents. One way to get discrete inputs for the DFT is to sample a continuous time function. Similarly, the duration of the discrete input function is finite. For this reason, the discrete Fourier transform is often cited as an essential tool for studying discrete-time functions with limited durations. DFT is well-suited for processing data stored in computers since it has a limited series of real or complex inputs. Digital Fourier transform (DFT) is extensively used in signal processing for frequency content analysis of sampled signals and convolution operations. Fast Fourier Transform (FFT) technique allows for fast computation of DFT in reality for the aforementioned applications, which is a significant enabling element. The Fast Fourier Transform (FFT) is now standard practice in several technical domains. The implementation of various communication systems is highly dependent on high speed FFT structures. Utilising an FFT processor for wireless communication enhances modern wireless technology with additional benefits such as reduced power consumption, increased speed, and so on. Thus, designing a high-performance FFT architecture is crucial to satisfy the real-time requirements. Building a new architecture for a 16-point Decimation in Frequency (DIF), Fast Fourier Transform (FFT) processor is the driving force behind this study. The most important factor is that we anticipate a more power-efficient FFT method if it meets the time requirements. Therefore, this is an effort to synthesise a DIF-FFT for 16-point inputs in Xilinx using the Verilog HDL design entity. In terms of speed and memory utilisation, the synthesis result demonstrates that the 16-point DIF-FFT processor is superior.

## **II. FAST FOURIER TRANSFORM ALGORITHM**

When it comes to effectively computing the discrete Fourier transform (DFT) and inverse discrete Fourier transform, one of the most helpful algorithms is the fast FFT technique. Since there are  $N$  data points to calculate, each of which requires  $N$  complex arithmetic operations, the number of complex multiplication and addition operations required by the simple forms of both the Discrete Fourier Transform (DFT) and the Inverse Discrete Fourier Transform (IDFT) is of order  $N^2$ . Discrete Fourier transformations of input signals may be computed using rapid Fourier transforms. The overall number of calculations required for DFT calculation is also decreased. In essence, Radix-2 offers two distinct algorithms: "Decimation in Time" (DIT) and "Decimation in Frequency" (DIF). The fundamental building block of these two algorithms is the recursive breakdown of  $N$ -point transformations.

A discrete Fourier transform with  $N$  points is split into two transforms with  $(N/2)$  points in this case. Any composite number ( $N$ ) may be processed in this way. Decomposition is straightforward if and only if  $N$  is a normal power of two and divisible by 2, but this procedure must be continued until we achieve the one point transform. The "Radix-2 decimation-in-frequency FFT algorithm" is being used to calculate discrete Fourier transforms in this case. This algorithm is likewise mostly based on the divide-and-conquer strategy.

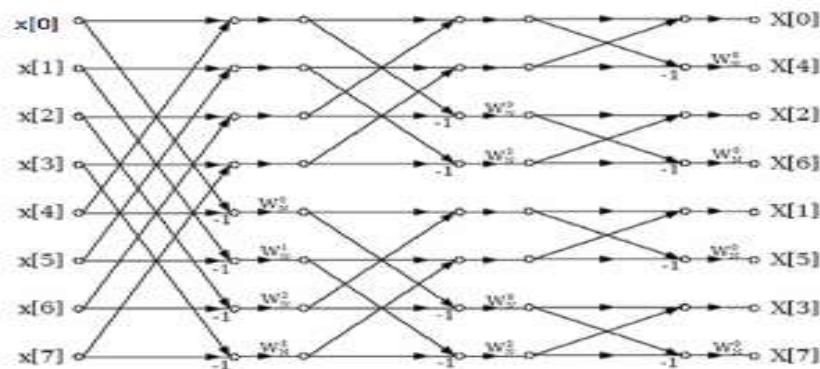

Figure 2.1 shows the whole eight-point radix-2 decimation frequency fast fourier transform method flow. Because it uses a lot less complicated multiplication and addition operations, the quick fourier transform essentially minimises the amount of processing needed. As seen in the image below, when the frequency is decimated, quick Fourier transform algorithms provide an output sequence that is bit reversal rather than in the original natural order.

**Figure 2.1: Decimation in Frequency fastfouriertransform algorithms for 8 point FFT Algorithm**

Discrete Fourier Transform is the primary function from which Fast Fourier Transform is formed. In contrast to FFT, which does the whole assessment all at once, significantly cutting down on computation time, typical direct method  $N$ -point DFT requires individual point evaluations. Four steps make up a 16-point fast Fourier transform (FFT) architecture based on Radix-2. From  $x[0]$  to  $x[15]$ , there are a total of sixteen possible input values.  $X(0)$  through  $X(15)$  are the values that are produced. The FFT butterfly structure provides the ability to add and subtract. The addition process is shown by the upward arrow in the butterfly structure. Similarly, the operation of subtraction will be shown by the downward arrow. The value that has been removed is multiplied by the twiddle factor value  $W_{KN}$  once again before moving on to the next step of processing. This calculation was completed simultaneously. It is common practice to use two operations of addition or subtraction and four actual multiplications when dealing with complex multiplication with the twiddle factor. FPGAs are the very attractive platform for high-speed digital signal processing, especially for radar technology [48, 49] but the implementation of the demanding signal processing algorithms as the FFT in the real time is complex because firstly the circuit structure must be designed and next implemented at the register-transfer level (RTL) using a hardware description language (HDL) such as VHDL and then synthesized and tested in the FPGA chip. However, do exists FFT IP cores, for example Xilinx [53] or Intel [54], but their configuration is difficult because of the required in-depth knowledge of the FFT core processor structure and arithmetic properties. This may make difficult the choice between the FPGA and digital signal processor such as TMS320C66x [15]. In order to simplify the design and implementation process the algorithmic approach was introduced by FPGA manufacturers. This approach is becoming more and more popular nowadays due to the accelerated design time and time-to-market (TTM). Large hardware projects pose major challenges in the design and verification of hardware at the HDL level. An increasing trend is observed as moving towards hardware acceleration to enhance performance of CPU-intensive tasks. It can be offloaded to hardware accelerator in FPGA. The HDL synthesis can be performed using behavioural or structural descriptions with Verilog or VHDL.

## Conclusion

This architecture has been used to successfully develop a new 16-point FFT processor for wireless applications that is both low-power and high-performance. The 16-point fast Fourier transform (FFT) is split into two 8-point FFTs, which form the basis of this design. In comparison to current designs, our suggested architecture for a very large scale integration (VLSI) based fast field-effect transistor (FFT) processor minimises the complexity level of the circuit. The suggested solution not only reduces the cost, size, and power dissipation for current wireless systems, but it also improves the computing efficiency of calculating the 16-point fast Fourier transform (FFT) in terms of memory utilisation and time delay.

## References

- [1] Brigham E.O., *The Fast Fourier Transform and its Applications*, Prentice-Hall, Inc., Englewood Cliffs, New Jersey, 1988.

- [2] Brandwood D., *Fourier Transforms in Radar and Signal Processing*, Artech House, 2003.

- [3] Rabiner L.R., Gold B., *Theory and Application of Digital Signal Processing*, Prentice-Hall, Inc., Englewood Cliffs, New Jersey, 1975.

- [4] Oppenheim A.V., Schafer R.W., *Digital Signal Processing*, Prentice-Hall, Inc., Englewood Cliffs, New Jersey, 1975.

- [5] Oppenheim A.V., Schafer R.W., *Discrete-Time Signal Processing*. Third Edition, Prentice-Hall, 2009.

- [6] McClellan J. H., Purdy R. J., *Applications of Digital Signal Processing*. PrenticeHall, 1978, (ch. 5, Applications of Digital Signal Processing to Radar).

- [7] Hwang T., Yang C., Wu G., Li S.G., Li Y., *OFDM and Its Wireless Applications: A Survey*, IEEE Transactions on Vehicular Technology, Volume. 58, Number 4, May 2009, pp. 1673-1694.

- [8] Chikada Y. et. al., *A very fast spectrum analyzer for radio astronomy*, International Conference on Acoustics, Speech and Signal Processing, Tokyo, 1986, pp. 2907- 2910.

- [9] Brezinski M.E, *Optical Coherence Tomography: Principles and Applications*, Elsevier, 2006.

- [10] Cooley J.W., Tukey J.W., *An algorithm for the machine calculation of complex Fourier series*, Mathematics of Computation., Volume. 19, pp. 297–301, 1965.

- [11] Abari O., Hamed E., Hassanieh H., Agarwal A., Katabi D., Chandrakasan A.P., Stojanovic V., *A 0.75-millionpoint fourier-transform chip for frequency-sparse signals*, 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), pp. 458–460, Feb. 2014.

- [12] Hopkinson T.M. Butler M, *A pipelined high-precision FFT architecture*, Mitre Corp., 1992.

- [13] Stratix IV, Altera Inc., 2014. [15] Texas Instruments, 6000TM high-performance and power efficient DSP, 2020.

- [14] Fialka O., Cadik M., *FFT and convolution performance in image filtering on GPU*, 10th Conference on Information Visualisation, 5-7 July, London, UK,

- [15] Bergland G.D., *Fast Fourier Transform Hardware Implementations -A Survey*, IEEE Transactions on Audio and Electroacoustics, Volume AU-17, Number 2, June 1969, pp. 109-119.

- [16] Wold E. H., Despain A. M., *Pipeline and parallel-pipeline FFT processors for VLSI implementations*, IEEE Transactions on Computers, Volume C-31, Number 5, pp. 414–426, May 1984.

- [17] Despain A. M., *Fourier transform computers using CORDIC iterations*. IEEE Transactions on Computers., Volume C-23, pp. 993-1001, Oct. 1974.

- [18] Swartzlander E. E., Young W. K. W, Joseph S. J., *A radix-4 delay commutator for fast Fourier transform processor implementation*, IEEE Journal. Solid-State Circuits, Volume 19, Number 5, pp. 702–709, Oct. 1984.

- [19] **Dharamveer, Samsher, Singh DB, Singh AK, Kumar N.** Solar Distiller Unit Loaded with Nanofluid-A Short Review. 2019;241-247. Lecture Notes in Mechanical

[20] **Dharamveer, Samsher.** Comparative analyses energy matrices and enviro-economics for active and passive solar still. materialstoday:proceedings. 2020.<https://doi.org/10.1016/j.matpr.2020.10.001>.

[21] **Dharamveer, SamsherKumar A.** Analytical study of  $N^{\text{th}}$  identical photovoltaic thermal (PVT) compound parabolic concentrator (CPC) active double slope solar distiller with helical coiled heat exchanger using CuO Nanoparticles. Desalination and water treatment. 2021;233:30-51.<https://doi.org/10.5004/dwt.2021.27526>

[22] **Dharamveer, Samsher, Kumar A.** Performance analysis of N-identical PVT-CPC collectors an active single slope solar distiller with a helically coiled heat exchanger using CuO nanoparticles. Water supply. 2021.<https://doi.org/10.2166/ws.2021.348>